3D Memory Chip

-

Home

-

3D Memory Chip

3D Memory Chip

The Memory Chip as a Multidimensional Portal: How Higher Dimensions Will Revolutionize Computing

The Hidden Architecture of Modern Memory

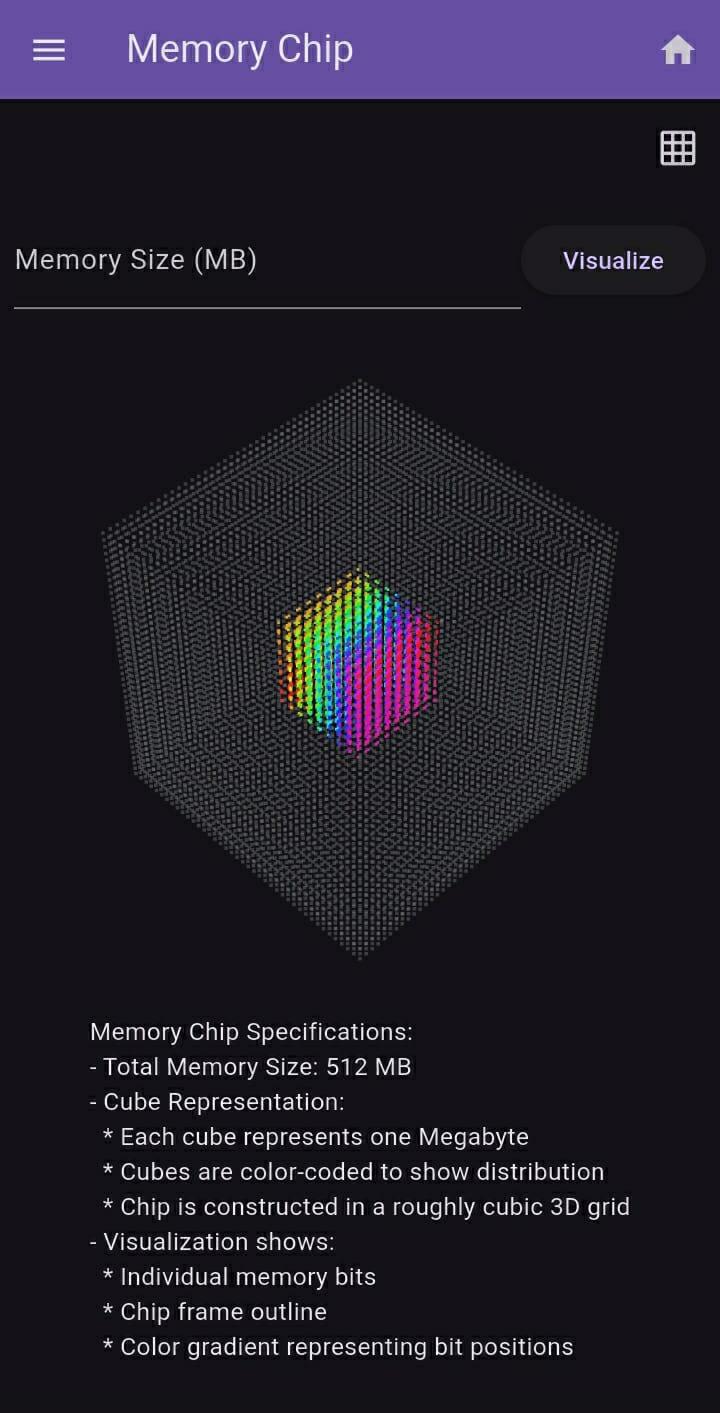

What appears as a simple 3D visualization of a memory chip actually represents something far more profound—a gateway to understanding how higher-dimensional concepts will transform computing. Each colored cube in our simulation represents not just a memory bit, but a node in a multidimensional information network that hints at the future of chip design.

The Fourth Dimension: Time as Memory's Canvas

The rotating animation reveals how memory operates across time:

Dynamic Data Flow: The rotation models how memory states evolve during computation cycles

Temporal Layering: Each position represents a different computational moment

4D Memory Architectures: Future chips may use temporal dimensions for data storage

This temporal dimension is already emerging in cutting-edge memory technologies like phase-change memory that use time-based states.

The Fifth Dimension: Probability in Memory States

The color gradients represent deeper quantum realities:

Probabilistic Bits: Qubit-like states where colors represent superposition

Error Correction: Distributed memory across probability spaces

Thermal Landscapes: Heat distribution as an extra information dimension

Future memory chips may exploit these probabilistic dimensions for quantum error correction and ultra-dense storage.

The Sixth Dimension: Parametric Memory Design

The adjustable parameters reveal a design revolution:

Scalable Architectures: Memory that grows in multiple dimensions

Self-Assembling Structures: Nano-scale cubes that configure themselves

Morphable Hardware: Chips that reshape for different tasks

This parametric approach anticipates programmable matter and liquid-phase computing.

The Seventh Dimension: Hyperdimensional Computing

The cubic lattice suggests extraordinary possibilities:

8D Memory Cells: Using all 8 corners of cubes as simultaneous states

Fractal Memory: Self-similar structures at nano and macro scales

Topological Protection: Data stored in knot-like higher-dimensional structures

Researchers are already exploring these concepts in topological quantum computing.

The Future of Multidimensional Chips

This visualization points toward several coming breakthroughs:

4D Stacking: Chips with active temporal layers for time-domain computing

Probabilistic Architectures: Memory that stores likelihoods rather than binary states

Self-Organizing Cubes: Nanoscale memory elements that assemble into optimal configurations

Hyperdimensional Addressing: Memory locations specified through 8D+ coordinate systems

The Path Forward

As we push against the limits of Moore's Law, the solution lies not in making smaller 2D chips, but in expanding into higher dimensions:

2025-2030: Commercial 3D stacked memory with temporal access

2030-2035: Probabilistic memory chips for AI applications

2035+: Topologically protected quantum memory cubes

The memory chip of the future won't be a flat wafer—it will be a multidimensional information sculpture, and this simple visualization gives us our first glimpse of that revolutionary architecture.

Share this service: